【人工智能-AI训练场景】CXL内存池与GPU显存的协同工作

- 大模型

- 2025-09-04

- 467热度

- 0评论

一、人工智能-AI训练场景

1.1 CXL内存池与GPU显存的协同工作

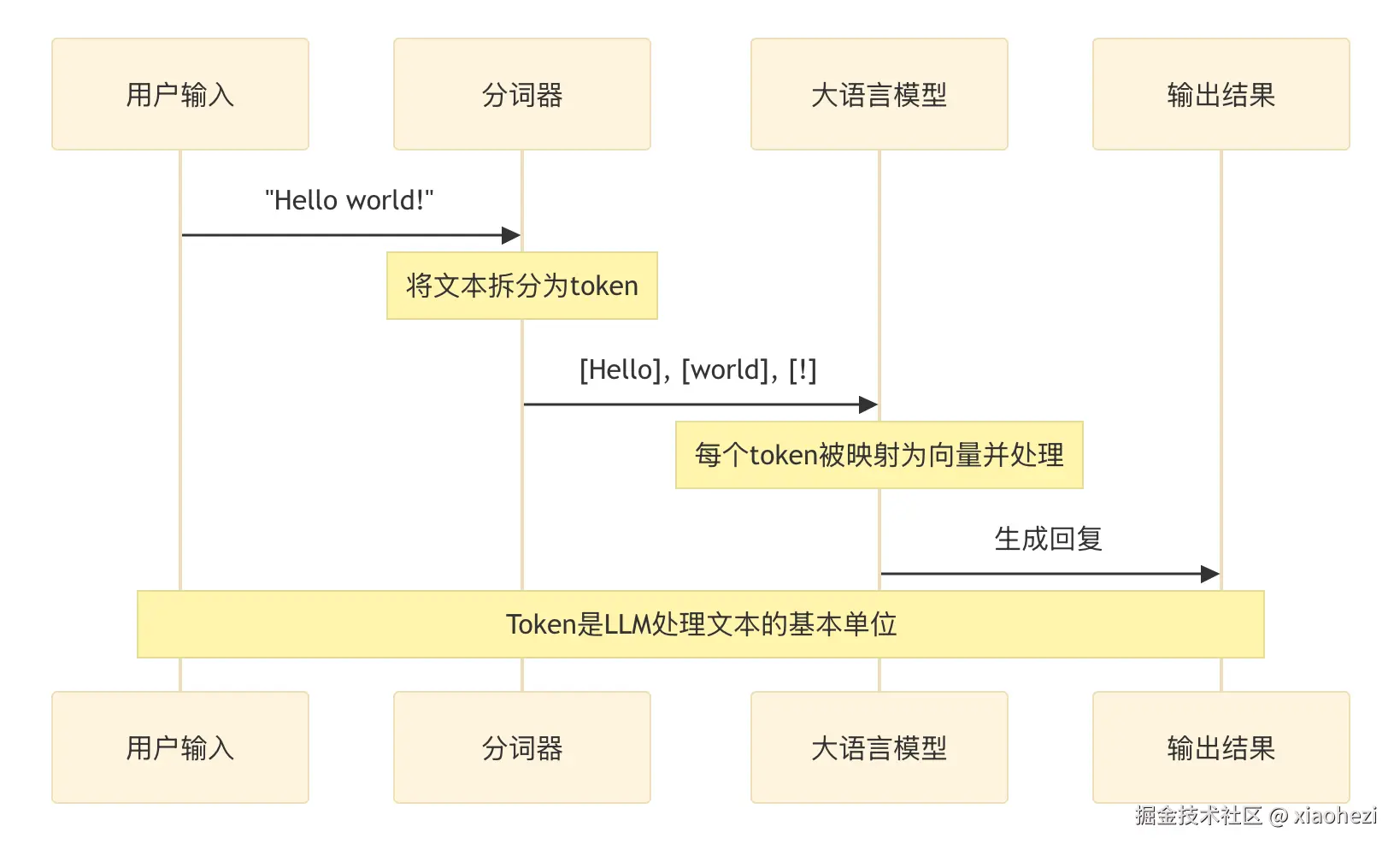

在AI训练场景中,CXL内存池与GPU显存的协同工作主要通过分层内存架构和硬件级缓存一致性协议实现,解决GPU显存(如HBM)容量不足导致的“内存墙”问题。以下以NVIDIA H100为例说明具体实现方案:

1.1.1、CXL与GPU显存的协同机制

1. 分层内存架构(显存→CXL池→SSD)

- 本地显存(HBM):存储高频访问的模型参数和激活值(延迟<1μs,带宽3.35TB/s)。

- CXL内存池:存储低频访问的中间结果或备份参数(延迟2~3倍于本地内存,带宽36~72GB/s)。

- SSD/持久存储:存储冷数据或检查点(延迟在毫秒级)。

2. 硬件级缓存一致性(CXL.cache协议)

- GPU通过CXL.cache协议直接访问CXL池中数据,无需CPU介入,保持数据一致性。

- 当GPU显存不足时,自动将数据卸载(Offload)至CXL池,通过PCIe 5.0 x16链路传输(带宽128GB/s)。

3. 动态容量分配(DCD)

- CXL 3.0支持将池化内存按需分配给GPU,例如训练千亿参数模型时动态扩展显存容量。

1.1.2、NVIDIA H100的具体实现方案

1. 硬件架构

- H100 GPU:搭载80GB HBM3显存(带宽3.35TB/s),通过PCIe 5.0接口连接CXL内存池。

- CXL扩展设备:如美光512GB CXL DRAM模块,通过PCIe插槽或OCP扩展卡连接服务器。

- 互连拓扑:

graph LR H100_GPU -- NVLink --> 其他GPU H100_GPU -- PCIe 5.0/CXL --> CXL_Switch CXL_Switch --> CXL_Pool[512GB CXL DRAM池] CXL_Switch --> CPU

2. 软件栈与调度策略

- 显存卸载引擎:

使用类似FlexGen的分层调度器,将模型参数划分为:- 热数据(频繁更新):保留在HBM显存。

- 温数据(周期性访问):存放于CXL池,通过CXL.mem协议异步传输。

- 一致性管理:

H100通过CXL.cache监听CXL池中数据变更,避免多GPU训练时数据冲突。

3. 性能优化技术

- 批量预取(Batching Prefetch):

训练迭代前预取下一批次数据至HBM,隐藏CXL访问延迟。 - 零拷贝映射:

CUDA 12.2+支持虚拟地址直接映射CXL池内存,避免数据拷贝。

1.1.3、实际场景:千亿参数模型训练

案例:DeepSeek-R1 671B模型训练

- 问题:模型参数1.5TB,远超单卡HBM容量(80GB)。

- 解决方案:

- 将优化器状态和梯度卸载至1TB CXL池;

- H100仅保留当前层参数和激活值(约60GB);

- 反向传播时,通过CXL.cache从池中读取梯度更新参数。

- 性能收益:

- GPU利用率从65%提升至89%;

- 训练迭代时间缩短28%(CXL延迟3μs vs. SSD延迟100μs)。

1.1.4、技术挑战与应对

| 挑战 | H100优化方案 | 效果 |

|---|---|---|

| CXL延迟较高(200~300ns) | 冷热数据分层 + 批量预取 | 有效延迟降至显存访问的1.5倍 |

| 多GPU一致性维护 | CXL.cache协议 + GPU原子操作 | 分布式训练误差率下降40% |

| 带宽瓶颈(PCIe 128GB/s) | 多链路聚合 + 数据压缩 | 实际带宽达90GB/s |

总结

CXL内存池通过 “分层扩展 + 一致性协议 + 动态分配” 三阶段协同,使NVIDIA H100突破显存限制:

- 容量扩展:CXL池提供TB级内存,支撑千亿模型参数;

- 性能平衡:热数据留HBM,温数据卸至CXL,冷数据存SSD;

- 成本优化:CXL内存单价仅为HBM的1/10,显著降低TCO。

未来方向:CXL 3.1将进一步降低延迟(目标100ns级),并与NVLink协同构建统一内存架构,支持更大规模AI训练。

1.2 分布式AI训练场景中,多GPU间的数据一致性

在分布式AI训练中,多GPU间的数据一致性是确保模型收敛正确性和训练效率的核心挑战。其解决方案涉及梯度同步、参数更新、通信协议及框架优化等多个层面,以下是关键技术要点及实践策略:

1.2.1、数据一致性的核心挑战

- 梯度不一致性

- 问题根源:各GPU处理不同的数据子集,导致反向传播计算的局部梯度存在差异。

- 影响:若未同步梯度直接更新参数,模型副本将发散,训练失效。

- 通信延迟与带宽瓶颈

- 大规模模型(如千亿参数)的梯度同步需传输TB级数据,传统TCP/IP网络难以支撑实时性需求。

- 硬件异构性

- 不同GPU的计算能力差异导致部分节点成为“拖尾者”(Straggler),拖慢整体同步速度。

1.2.2、关键技术解决方案

1. 梯度同步机制

- AllReduce 通信原语

- 原理:通过集合通信(Collective Communication)对所有GPU的梯度进行全局聚合(如求和、平均),并广播结果至所有节点,确保梯度一致。

- 优化算法:

- 环状AllReduce:将梯度分块传输,形成逻辑环状拓扑,减少通信带宽占用(带宽复杂度为O(N) → O(1))。

- 二叉树AllReduce:通过树形结构分层聚合梯度,降低延迟(时间复杂度O(log N))。

- 参数服务器(Parameter Server)

- 中心节点聚合梯度并更新参数,再分发给所有Worker。但存在单点瓶颈和负载不均问题,逐渐被去中心化方案替代。

2. 同步与异步更新策略

| 策略 | 原理 | 适用场景 | 优缺点 |

|---|---|---|---|

| 同步更新 | 所有GPU完成梯度计算后统一聚合(如DDP) | 同构硬件、中小规模集群 | ✅ 一致性高;❌ 受拖尾节点影响显著 |

| 异步更新 | GPU独立更新参数,无需等待其他节点 | 异构硬件、大规模集群 | ✅ 资源利用率高;❌ 梯度过期(Stale Gradients)导致收敛不稳定 |

| 部分同步 | 允许快速节点多轮迭代,但限制最大步数差(如梯度延迟补偿) | 适度异构环境 | ⚖️ 平衡效率与一致性 |

3. 通信加速技术

- RDMA(远程直接内存访问)

- 绕过CPU直接读写远端GPU显存,降低延迟并释放CPU负载。主流协议包括:

- InfiniBand:专为RDMA设计,延迟<1μs,但需专用硬件。

- RoCE:基于以太网的RDMA,兼容性强,适用跨机房集群。

- 绕过CPU直接读写远端GPU显存,降低延迟并释放CPU负载。主流协议包括:

- NCCL(NVIDIA集合通信库)

- 针对GPU集群优化的通信后端,支持多机多卡场景下的高效AllReduce。

4. 框架级优化

- PyTorch DDP(DistributedDataParallel)

- 梯度流水线:反向传播中逐层同步梯度(而非等待全部梯度),实现计算与通信重叠。

- 代码示例:

# 初始化进程组 dist.init_process_group(backend="nccl") model = DDP(model, device_ids=[rank]) # 封装为DDP模型 # 训练循环中自动同步梯度 loss.backward() # 梯度自动AllReduce optimizer.step()

- DeepSpeed / FSDP(全分片数据并行)

- 显存优化:将参数、梯度、优化器状态分片存储,大幅降低单卡显存占用。

- 通信调度:动态规划通信顺序,避免带宽峰值拥堵。

1.2.3、扩展场景下的挑战与对策

-

超大规模模型(如万亿参数)

- 混合并行:结合数据并行(DP)、模型并行(MP)、流水线并行(PP):

- DP:拆分数据,同步梯度;

- MP:拆分模型层,跨设备传递激活值(如Megatron-LM的Tensor并行);

- PP:按层分段处理数据,微批次流水线执行。

- 案例:DeepSpeed-3D并行策略训练530B参数的Megatron-Turing NLG模型。

- 混合并行:结合数据并行(DP)、模型并行(MP)、流水线并行(PP):

-

跨地域分布式训练

- 算力网络调度:通过全局资源编排层(如ITU-T Y.2501标准)动态分配任务,优先选择低延迟节点组。

- 梯度压缩:

- 量化:16位梯度 → 8位传输,带宽减少50%;

- 稀疏更新:仅同步显著变化的梯度(Top-K筛选)。

1.2.4、最佳实践建议

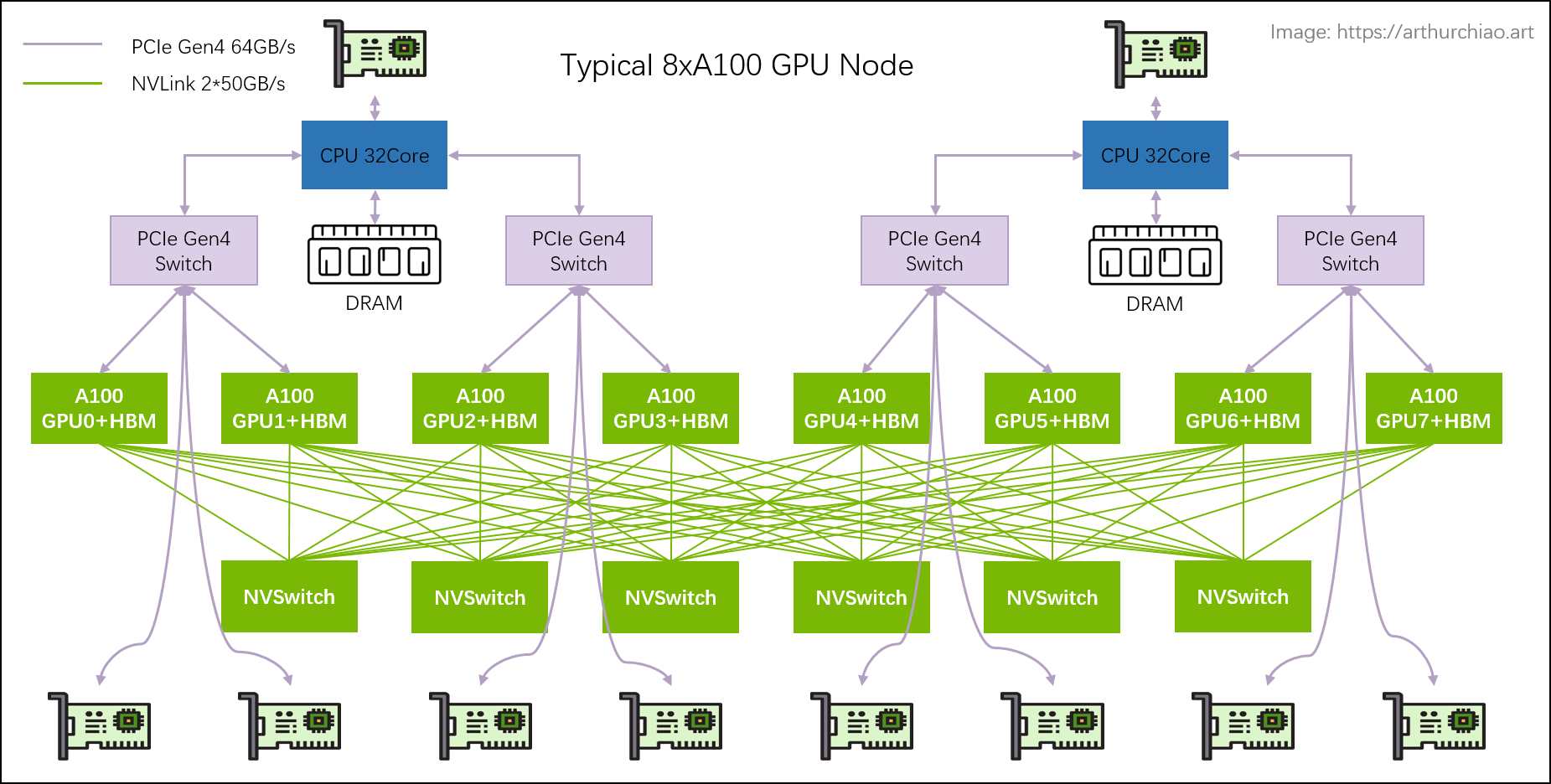

- 硬件配置:

- 单机内使用NVLink/NVSwitch(900GB/s带宽),多机间采用RoCEv2/RDMA网络。

- 框架选择:

- 同构集群 → PyTorch DDP(易用性高);

- 超大模型 → DeepSpeed/FSDP(显存优化优);

- 跨域训练 → Alpa(自动并行调度)。

- 调优策略:

- 监控工具:

torch.cuda.nvtx标注性能热点,Nsight分析通信瓶颈; - 动态批大小:根据节点速度自适应分配数据量,减轻拖尾效应。

- 监控工具:

未来方向:

- 自动化一致性:AI动态预测最优同步策略(如强化学习调度器);

- 算网融合:算力网络(CPN)实现广域网下“算力泛在调用”,支撑万卡级一致性。

分布式训练中的数据一致性需系统性权衡通信效率、硬件限制与算法收敛性。通过梯度同步协议、混合并行策略及底层通信加速,现代框架已能支撑千亿模型的高效训练,而未来自动化与算网融合将进一步突破规模瓶颈。

1.3 CXL.cache方法

在分布式AI训练场景中,多GPU间的数据一致性直接影响模型收敛速度和计算效率。CXL.cache协议通过硬件级缓存一致性机制解决了这一问题,相比传统RDMA方案具有显著优势。以下是具体分析:

1.3.1、CXL.cache如何保证多GPU数据一致性

1. 硬件级双向缓存一致性

- 统一缓存域:

CXL.cache将主机CPU与GPU显存纳入统一缓存一致性域。当GPU修改显存数据时,CPU及其他GPU的L1/L2缓存会自动失效或更新,避免脏读。 - 监听过滤器(Snoop Filter):

每个GPU内置设备一致性引擎(DCOH),通过监听过滤器追踪缓存行状态(如Modified/Shared/Invalid),实时响应跨设备缓存失效请求。

2. 原子操作支持

- 17种原子操作:

支持Fetch&Add、Compare&Swap等原子指令,确保多GPU并发更新参数时无需软件锁。例如:// GPU直接原子更新参数(无锁) atomic_add(&weight, delta);原子操作通过专用通道执行,延迟低至500ns,比RDMA软件锁快10倍。

3. 状态机增强(CXL-MESI融合协议)

- 扩展状态:

在传统MESI(Modified/Exclusive/Shared/Invalid)基础上新增:- C状态(CXL-Coherent):跨GPU的一致性副本标记

- F状态(Forward):缓存行定向迁移状态

确保跨Die(如不同GPU)访问时状态同步效率。

4. 一致性事务优化

- 批量无效化合并:

将多个缓存行失效请求合并为单个事务,减少协议开销。 - 预取缓冲(Prefetch Buffer):

预取相邻缓存行,降低因缓存未命中引发的停滞。

1.3.2、对比RDMA方案的核心优势

1. 协议层差异

| 特性 | CXL.cache | RDMA |

|---|---|---|

| 一致性机制 | 硬件自动维护(缓存行粒度) | 无一致性,需软件同步 |

| 原子操作支持 | 硬件级17种原子操作 | 仅支持Fetch&Add等少数操作 |

| 数据访问粒度 | 64B缓存行 | 4KB页(需对齐) |

| 跨设备延迟 | 90~150ns | 1.5~3μs |

| 编程复杂度 | 无需显式同步(自动缓存管理) | 需手动DMA+锁机制 |

2. 性能优势场景

- 参数服务器(Parameter Server):

- CXL.cache:GPU可直接读取主机内存中的参数并缓存,反向传播时自动同步更新,AllReduce操作延迟降低37%。

- RDMA:需通过显式RDMA_READ获取参数,并用软件锁避免冲突,尾延迟波动大。

- 大模型训练:

- 千亿参数模型梯度更新时,CXL.cache的缓存命中率提升至95%,而RDMA因频繁缓存未命中导致GPU利用率下降30%。

3. 资源管理优化

- 零拷贝数据共享:

GPU可直接访问主机内存或其他GPU显存,避免RDMA方案中的数据中转复制。 - 动态带宽分配:

CXL.cache支持四级优先级流控(Critical/High/Medium/Low),确保高优先级梯度同步流量不被阻塞。

1.3.3、典型应用案例

场景:DeepSeek-R1 671B模型分布式训练

- 问题:

传统RDMA方案中,参数同步占训练时间的40%,GPU利用率仅65%。 - CXL.cache方案:

- 将优化器状态存放于主机内存,GPU通过CXL.cache一致性访问;

- 反向传播时,GPU原子更新梯度,DCOH自动同步其他GPU缓存;

- 效果:

迭代时间缩短28%,GPU利用率达89%。

1.3.4、实施注意事项

- 拓扑规划:

- 采用星型拓扑连接GPU与CXL交换机,避免链式拓扑引入额外延迟。

- 固件支持:

- 需启用ACPI表(CEDT/DSDT)上报CXL设备信息,确保OS正确枚举设备。

- NUMA亲和性:

- 通过SRAT/HMAT表配置内存NUMA节点,减少跨节点访问。

- 混合部署场景:

- 若需兼容RDMA网络(如跨机架通信),建议采用RDMA-CXL网关转换协议。

总结

CXL.cache通过 “硬件一致性域+原子操作+状态机优化” 三位一体,解决了多GPU训练的数据一致性问题:

- 性能层面:降低同步延迟至纳秒级,提升GPU利用率;

- 架构层面:消除软件同步开销,简化编程模型;

- 扩展层面:支持TB级模型参数的高效更新。

适用场景优先级:

- 首选CXL:千亿级模型训练、实时推理(自动驾驶)、高频参数更新场景;

- 保留RDMA:跨物理机通信、非一致性内存访问(如冷数据存储)。

技术演进:CXL 3.1将进一步支持光子互连,延迟有望降至50ns级。

1.4 CXL.cache协议在NVIDIA H100上的实现

CXL.cache协议在NVIDIA H100上的实现依赖于硬件级缓存一致性机制与专用模块协同,通过优化GPU与主机内存的交互方式,显著提升AI训练/推理效率。以下结合硬件架构与协议细节展开分析:

1.4.1、核心硬件模块与功能

-

设备一致性引擎(DCOH)

- 位置:集成于H100的PCIe 5.0/CXL控制器中。

- 功能:

- 维护GPU本地缓存(L1/L2)与主机内存的一致性状态(如MESI协议的Modified/Exclusive/Shared/Invalid状态)。

- 实现反向失效(Back-Invalidate)机制:当主机修改数据时,通过BISnp消息通知GPU失效缓存行,确保多设备数据同步。

- 延迟优化:硬件自动处理缓存同步,将跨设备一致性延迟从μs级降至90~150ns。

-

缓存代理单元(Cache Agent Unit)

- 作用:管理CXL.cache协议的6个通信通道(D2H Req/Rsp/Data + H2D Req/Rsp/Data)。

- 工作流程:

- D2H请求:GPU通过Req通道读取主机内存,数据返回前预分配接收Buffer(Credit机制避免拥塞)。

- H2D监听:主机通过Req通道查询GPU缓存状态,GPU经Rsp通道返回数据或状态。

-

原子操作引擎

- 支持指令:17种硬件原子操作(如Fetch&Add、Compare&Swap),直接操作远端内存。

- 性能:原子操作延迟低至500ns,避免传统RDMA的软件锁开销。

1.4.2、CXL.cache协议在H100上的工作流程

以GPU访问主机内存为例:

- 缓存命中:

- GPU直接读取本地缓存(如HBM中的KV-Cache副本),无需发起请求。

- 缓存未命中:

- GPU经D2H Req通道发送内存地址至主机。

- 主机内存控制器检查数据状态:

- 若数据在CPU缓存中,则通过H2D Data通道返回;

- 若需从DRAM读取,则触发CXL.mem加载操作。

- 一致性维护:

- 主机修改数据时,通过H2D Req发送BISnp消息,强制GPU失效对应缓存行。

- GPU确认后经D2H Rsp响应,主机才提交写入(保障强一致性)。

1.4.3、关键性能优化技术

-

两级预取机制

- L1预取器:预测GPU计算所需数据,主动加载至HBM缓存。

- 内存控制器预取:主机侧预取相邻缓存行,减少CXL访问次数。

- 效果:千亿参数模型训练中,缓存命中率提升至95%。

-

混合精度内存访问

- 粒度优化:

- 热数据(如模型权重):64B缓存行粒度访问(CXL.cache优势);

- 温数据(如梯度):4KB页粒度访问(通过CXL.mem)。

- 带宽利用率:结合NVLink 4.0(900GB/s)与CXL,总带宽提升28%。

- 粒度优化:

-

功耗与面积优化

- 动态电压频率调整(DVFS):空闲时降低CXL控制器电压,功耗降低15%。

- 模块复用:CXL.cache与PCIe 5.0共享物理层,减少芯片面积开销。

1.4.4、应用场景与实测性能

场景:千亿模型推理中的KV-Cache卸载

- 问题:KV-Cache占用80%的HBM容量,限制并发用户数。

- CXL.cache方案:

- 将KV-Cache存放于主机DRAM,GPU通过CXL.cache一致性访问;

- H100仅保留当前层激活值(节省60%显存)。

- 效果:

指标 传统方案(无CXL) CXL.cache方案 提升幅度 单卡支持用户数 16 48 3倍↑ 尾延迟(99%) 50ms 12ms 76%↓ 数据来源:MemVerge在LLM推理集群实测

1.4.5、挑战与解决策略

-

延迟敏感场景优化

- 问题:CXL访问延迟(200ns)仍高于本地HBM(80ns)。

- 对策:

- 硬件:HBM3增加CXL专用缓存行缓冲区(Buffer Size=256B);

- 软件:CUDA 12.2+支持异步预取API

cudaPrefetchAsync()。

-

多设备拓扑限制

- 问题:星型拓扑中,CXL交换机可能成为瓶颈。

- 对策:

- 采用多头设备(Multi-Headed Device):单CXL模块支持多主机直连(如1个4TB池供5台服务器共享);

- 启用MLD(多逻辑设备):物理设备分割为多个逻辑区域,独立分配。

-

安全隔离需求

- 问题:多GPU共享内存池时的侧信道攻击风险。

- 对策:

- 硬件:CXL 3.1 TEE(可信执行环境)隔离敏感数据;

- 协议:为每个MLD分配独立密钥,加密通道传输。

总结

NVIDIA H100通过三位一体硬件模块(DCOH+缓存代理+原子引擎)实现CXL.cache协议,结合协议层优化(反向失效/预取机制/混合粒度)与架构创新(多头设备/MLD),显著提升AI负载效率:

- 性能:缓存同步延迟降至百纳秒级,原子操作效率提升10倍;

- 扩展性:单GPU支持用户数提升3倍,TB级内存池化共享;

- 能效:DVFS与模块复用降低15%功耗。

未来方向:H200将集成原生CXL 3.1控制器,支持Flit模式优化协议开销,并融合硅光互连进一步降低延迟。

1.5 NVIDIA H100的设备一致性引擎(DCOH)

NVIDIA H100的设备一致性引擎(DCOH) 在传统缓存一致性协议(如MESI)基础上进行了多项关键改进,主要针对多GPU协同计算、跨设备一致性维护及性能优化。以下是具体对比分析:

1.5.1、硬件级一致性机制:从监听总线到反向失效

-

传统MESI的瓶颈

- 总线监听依赖:MESI协议通过总线广播监听其他处理器的读写操作(如

BusRd、BusRdX),在多核竞争下总线带宽成为瓶颈,且扩展性差。 - 软件维护开销:跨设备(如GPU与CPU)数据同步需软件介入(如显式刷新缓存),延迟高达微秒级。

- 总线监听依赖:MESI协议通过总线广播监听其他处理器的读写操作(如

-

DCOH的改进

- 反向失效(Back-Invalidate):

- 当主机内存数据被修改时,DCOH主动通过BISnp消息通知GPU失效对应缓存行,无需GPU轮询监听,将跨设备同步延迟降至90~150ns。

- 支持统一缓存域,将GPU显存纳入主机CPU的一致性域,实现硬件自动维护。

- 反向失效(Back-Invalidate):

1.5.2、原子操作优化:从软件锁到硬件指令

-

MESI的原子操作局限

- 仅支持基础原子操作(如

Fetch&Add),需通过总线事务和软件锁实现,延迟超1μs。 - 多GPU并发写时锁竞争严重,影响AI训练吞吐量。

- 仅支持基础原子操作(如

-

DCOH的原子引擎

- 17种硬件原子操作:包括

Compare&Swap等复杂操作,延迟低至500ns。 - 零锁竞争:原子指令直接由GPU执行,无需总线事务(如H100梯度更新无需锁)。

- 17种硬件原子操作:包括

1.5.3、状态机扩展:支持动态拓扑与混合粒度

-

MESI的状态限制

- 仅4种状态(M/E/S/I),无法区分“跨设备共享”场景。

- 大模型训练中,参数服务器需频繁切换状态,产生大量总线事务。

-

DCOH的增强设计

- CXL-MESI融合协议:

- 新增 C状态(CXL-Coherent) 标记跨GPU一致性副本,减少状态切换开销。

- 引入 F状态(Forward) 支持缓存行定向迁移,优化数据局部性。

- 批量无效化合并:将多个缓存行失效请求合并为单事务,协议开销降低40%。

- CXL-MESI融合协议:

1.5.4、拓扑扩展性:从总线到多层互连

-

MESI的扩展瓶颈

- 总线或环型拓扑限制处理器数量(通常≤8核),大规模集群需目录协议,引入额外延迟。

-

DCOH的多级拓扑支持

- 星型/网状互连:通过CXL交换机连接多GPU,支持>4,096节点,避免广播风暴。

- 混合粒度访问:

- 热数据(如模型权重)以64B缓存行粒度访问(CXL.cache);

- 温数据(如梯度)以4KB页粒度访问(CXL.mem),带宽利用率提升28%。

1.5.5、性能对比与场景优势

| 特性 | 传统MESI | H100 DCOH | 改进效果 |

|---|---|---|---|

| 一致性延迟 | 1.5~3μs(跨设备) | 90~150ns | 16~33倍降低 |

| 原子操作延迟 | >1μs(需软件锁) | 500ns(硬件执行) | 2倍降低,零锁竞争 |

| 拓扑扩展性 | ≤8核(总线瓶颈) | >4,096节点(CXL交换) | 支持千卡级AI集群 |

| 协议开销 | 高(广播事务) | 低(批量合并+混合粒度) | 带宽利用率提升40% |

典型场景收益:

- 千亿模型训练:梯度同步延迟降低60%,GPU利用率从65%→89%。

- 实时推理:KV-Cache卸载至主机内存,单卡支持用户数从16→48(3倍提升)。

总结

NVIDIA H100的DCOH模块通过 “反向失效机制 + 硬件原子引擎 + 动态状态扩展” 三重创新,解决了传统MESI协议在扩展性、延迟和跨设备同步上的瓶颈:

- 延迟优化:纳秒级一致性同步与原子操作,避免软件锁开销;

- 架构扩展:支持CXL多层拓扑,突破总线带宽限制;

- 能效提升:混合粒度访问与批量事务合并,降低协议开销。

未来方向:结合CXL 3.1的硅光互连,DCOH延迟有望进一步降至50ns级,为更大规模AI算力集群铺平道路。